FMラジオ用PLL-VFOの実験

※「PLL方式FMラジオの製作」でFMラジオを製作しました。(2010-01-05)

※「PIC18FでPLL-IC(TC9256P)の制御」でPICによるTC9256Pの制御をテストしました。(2010-01-20)

「PLL-VFOを使ったエアバンド受信機の製作」で使用したPLL-ICのMB87001Aは、1個あたりの単価が安いのは良いのですが、プリスケーラが内蔵されていません。そのため、単価の高いプリスケーラICのMB504を外付けで使用しています。今回、通販で東芝のPLL-IC TC9256Pを安く入手することが出来たので、AVRを使ってPLL-ICの制御実験をしてみました。

TC9256Pは、AM/FMラジオに使用することを想定されたもので、プリスケーラも内蔵されています。周波数は、0.5~150MHzまでと幅広い周波数に対応可能です。今回は、FMラジオに使用することを目標にして実験します。

前回のMB87001Aもそうでしたが、このTC9256Pも3線式シリアル通信で制御します。シリアル制御の方法は、データシートに詳しく記載されています。また、XKPのホームページさんのWebサイトに、このICの使い方が丁寧に解説されているので参考にしました。

最初は、FMフロントエンドICのTA7358APGで局部発振させて実験したのですが、発振が安定せず、断念しました。おそらくブレッドボードの環境が悪いと思われます。

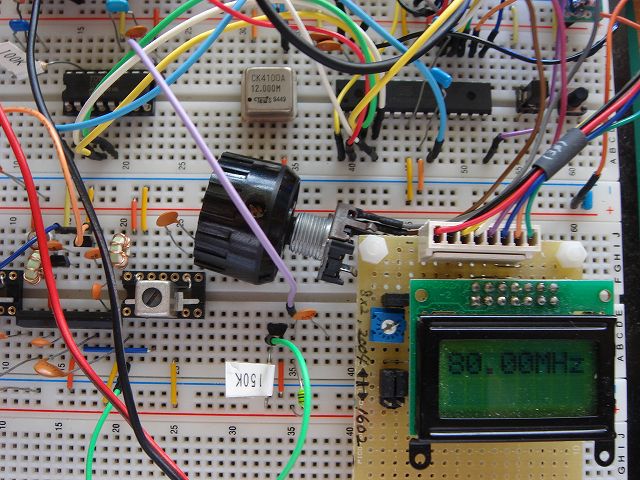

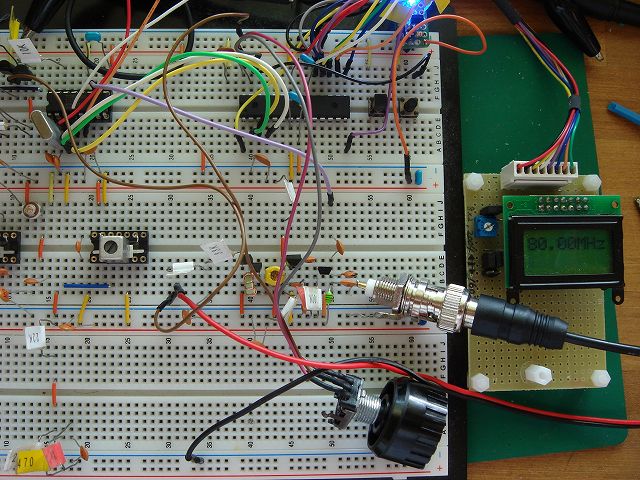

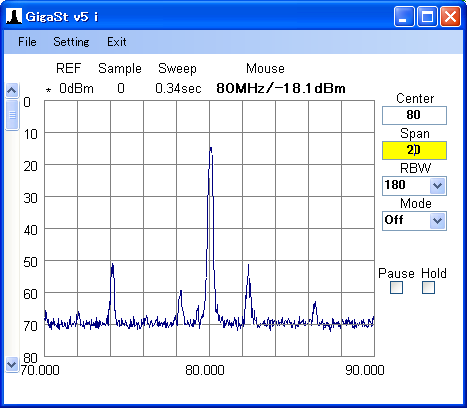

VCOとして普通のコルピッツ発振回路(クラップ発振回路)を使用してみると、ブレッドボード上でも安定して動作させることが出来ました。GigaStでスペクトラムを確認するとAVRのクロックのスプリアスと思われるものが確認できますが、発振周波数自体は安定しています。(・・・ただ、実際にFMラジオの局発として使用できるかどうかは別問題ですが・・)

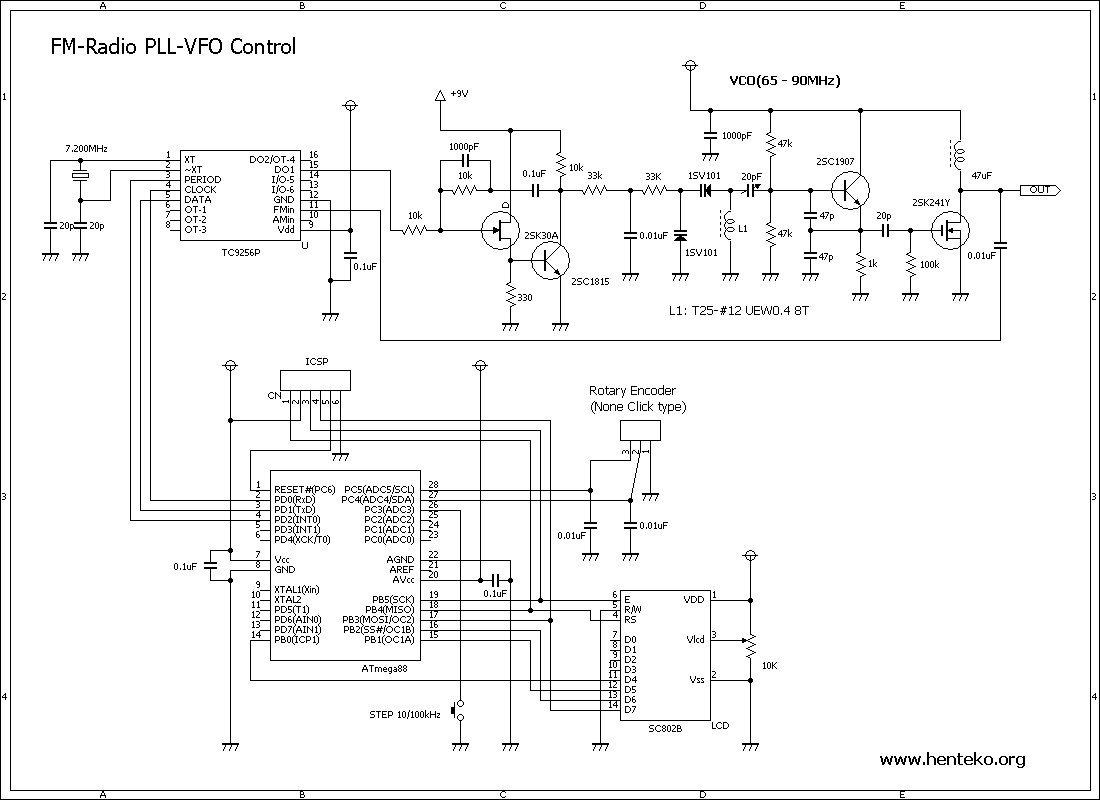

実験の回路図です。TC9256Pのデータシートでは動作に必要なクロック周波数が4種類に限定されています。今回は、ちょうど7.2MHzの水晶発振子が入手できたので使用しましが、先の「XKPのホームページ」さんによると、他の周波数のクロックも使えるようです。

位相比較する基準周波数を10KHz固定としました。周波数の可変最小ステップも10KHzとなりますが、FMラジオなら十分です。AVRのクロックは、速度と精度が必要ないので8MHzの内部クロック動作としました。

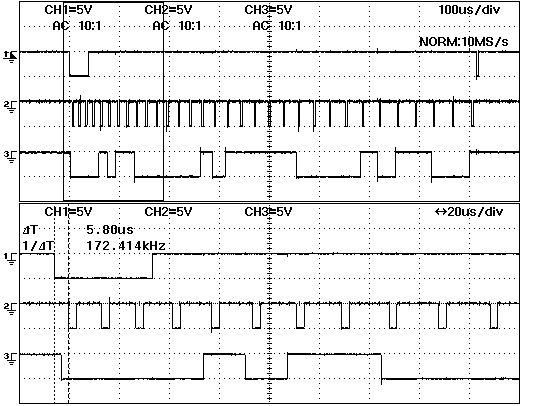

TC9256Pを周波数80.00MHzに制御するシリアル信号のタイムチャートをオシロでキャプチャしたものです。CH1は、ピリオド信号、CH2はクロック、CH3がデータとなっています。(下側は、上側のズームアップとなっています。)

データ列は、以下の32ビットのデータをLSBファーストで出力します。

レジスタアドレス(8ビット)=0xD0

プログラマブルカウントデータ(16ビット)=80MHz÷10KHz(基準周波数)=8000

リファレンスコード(4ビット)=10(1010)・・基準周波数10KHz

プログラマブルカウンタモード(2ビット)=1(01)・・FMパルススワロー方式

水晶発振子選択ビット(2ビット)=2(10)・・・7.2MHz

これらをLSBからのビット列であらわすと

0000 1011 0000 0010 1111 1000 0101 1001

となります。

なお、タイムチャートが次第に間延びしていくのは、プログラム中のビットシフトの桁数が多くなると処理に時間がかかるためと思われます。

AVRのプログラムです。AVRStudio4とWinAVR-20090313で作成しました。周波数の可変ステップは、ソフトウェアで10KHzと100KHzの切替としました。実際にFMラジオに使用するときは、以前作成した短波ラジオのVFOと同じようにAVRのフラッシュメモリを使った周波数メモリを実装する予定です。

2件のピンバック

PLL方式FMラジオの製作 | henteko.org

PIC18FでPLL-IC(TC9256P)の制御 | henteko.org

コメントは現在停止中です。