AVR-DDSでPLL-VFOの実験その2

この仕組みを利用した短波ラジオを「PLL-VFOを使った短波受信機の製作」で実際に作成しました。(2009-07-22)

「PIC-DDSの基礎実験」でPIC18Fを使ったDDSをテストしました。(2009-03-05)

前回の「AVR-DDSでPLL-VFOの実験」では、AVR-DDSから方形波を出力してPLLの基準周波数としました。サンプリング周波数を160kHzと高くしたのですが、方形波の波形が「なまる」ことを避けるためにローパスフィルタを使用していません。このため位相歪を含んだ出力となっていす。PLLからの最終出力(VCO出力)は、オシロスコープで波形を見る限りは大きな影響がないようですが、あまり気持ちのいいものではありません。

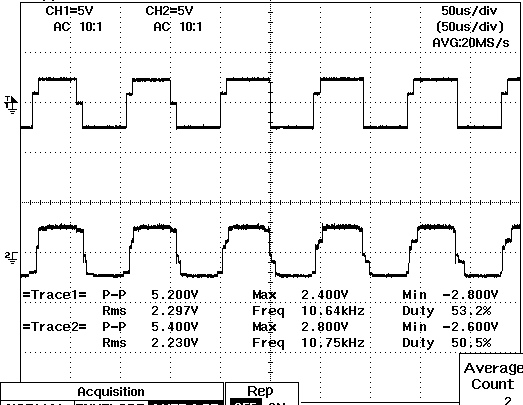

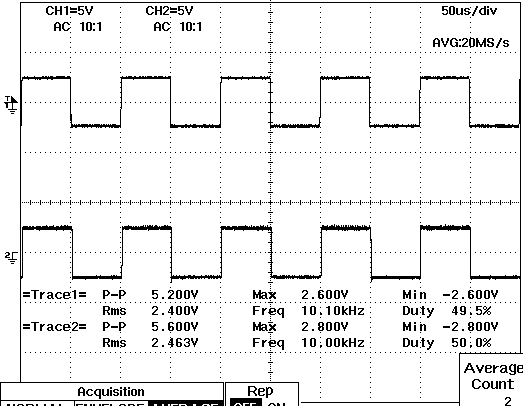

試しに位相比較器4046Bに入るAVR-DDSの出力と分周されたVCO出力の波形をオシロスコープでアベレージングして表示させると位相ずれにより、かなり歪んだ波形になります。

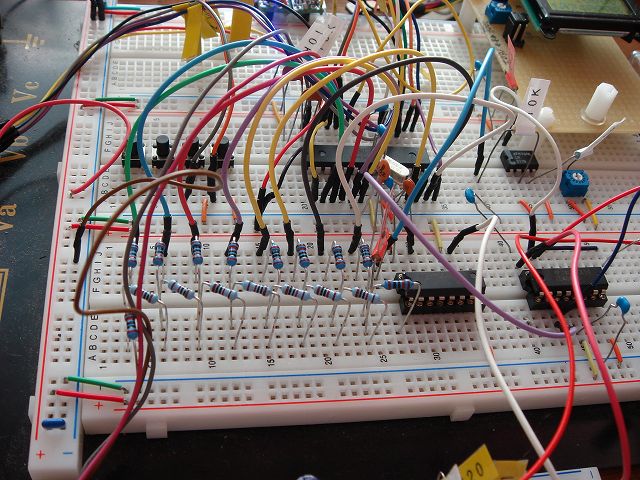

AVR-DDSの出力を正弦波として、ローパスフィルタを通せば、位相歪みの少ない波形が得られると思い実験してみました。AVR-DDSは、以前作成した「AVRを使ったDDS方式低周波発振器の製作」と同じくDACに8ビットのR-2Rラダー抵抗回路を使用します。

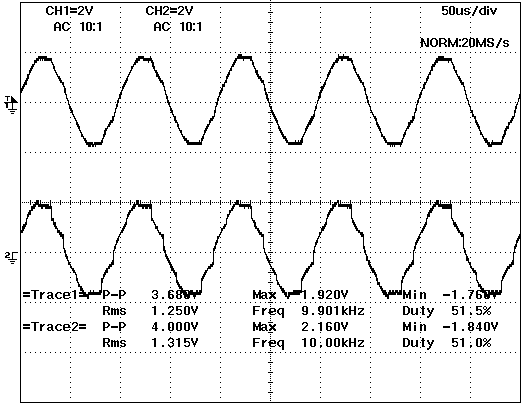

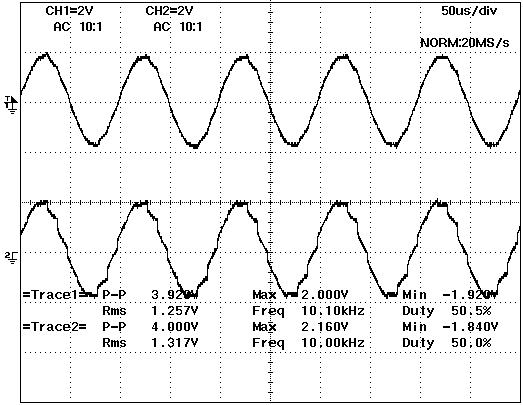

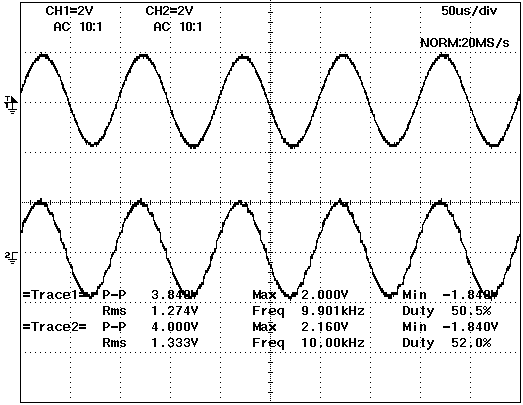

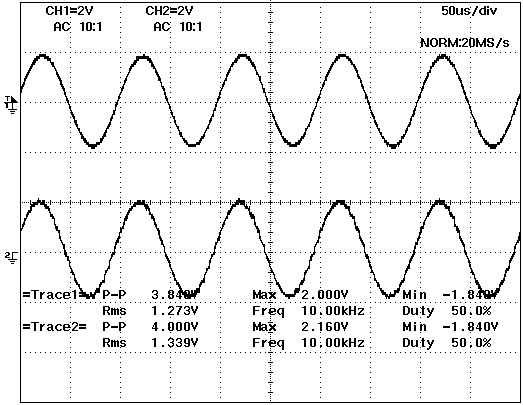

ローパスフィルタは、カットオフ周波数50kHzを目標に単純なCRフィルタとしました。AVR-DDSから10kHzを出力し、このフィルタを通した出力を、サンプリング周波数を変化させてオシロスコープで確認しました。左上から80kHz、100kHz、160kHz、200kHzでCH1がフィルタ通過波形、CH2がDAC出力波形です。

サンプリング周波数を高くすれば単純なローパスフィルタでも、きれいな波形が得られるようです。とりあえず、方形波の時と同じ160kHzを採用しますが、ローパスフィルタの設計次第では、80kHzでも、位相比較器への入力信号として十分だと思います。

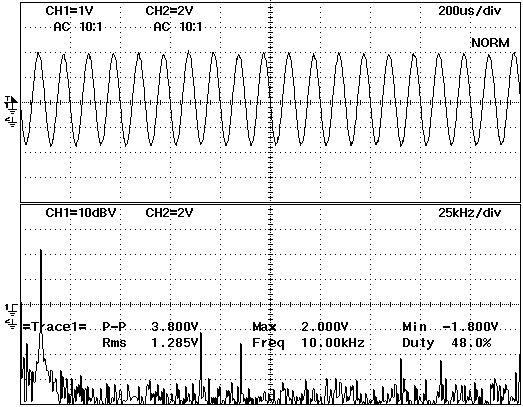

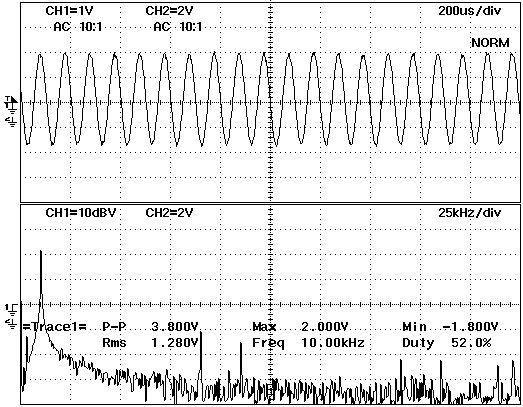

サンプリング周波数160kHzの時のAVR-DDSの出力する正弦波をオシロスコープでFFT解析してみました。左は、10000Hz、右は10051Hzのものです。波形テーブル参照時の小数点以下切捨てにより、位相歪が大きくなる場合は、出力スペクトルの裾野が盛り上がり波形ひずみが大きくなることがわかります。

4046Bの位相比較器は、入力信号の立ち上がりで位相比較しているようです。AVR-DDSの出力正弦波をそのまま入力しても、正常にPLLロックしますが、ノイズ等の影響でVCO出力に多少の周波数変動がありました。そこで、CMOSシュミットトリガインバータの74HC14で正弦波を方形波に変換して動作させるとVCO出力が安定することが確認できました。

正弦波から方形波への変換でコンパレータICのLM311でも、試してみましたが同じように安定して動作します。また、CMOSインバータの74HC04では、PLLがロックしませんでした。

位相比較器に入る比較対象波形をオシロスコープでアベレージングして表示させてみましたが、大きな歪は見られません。

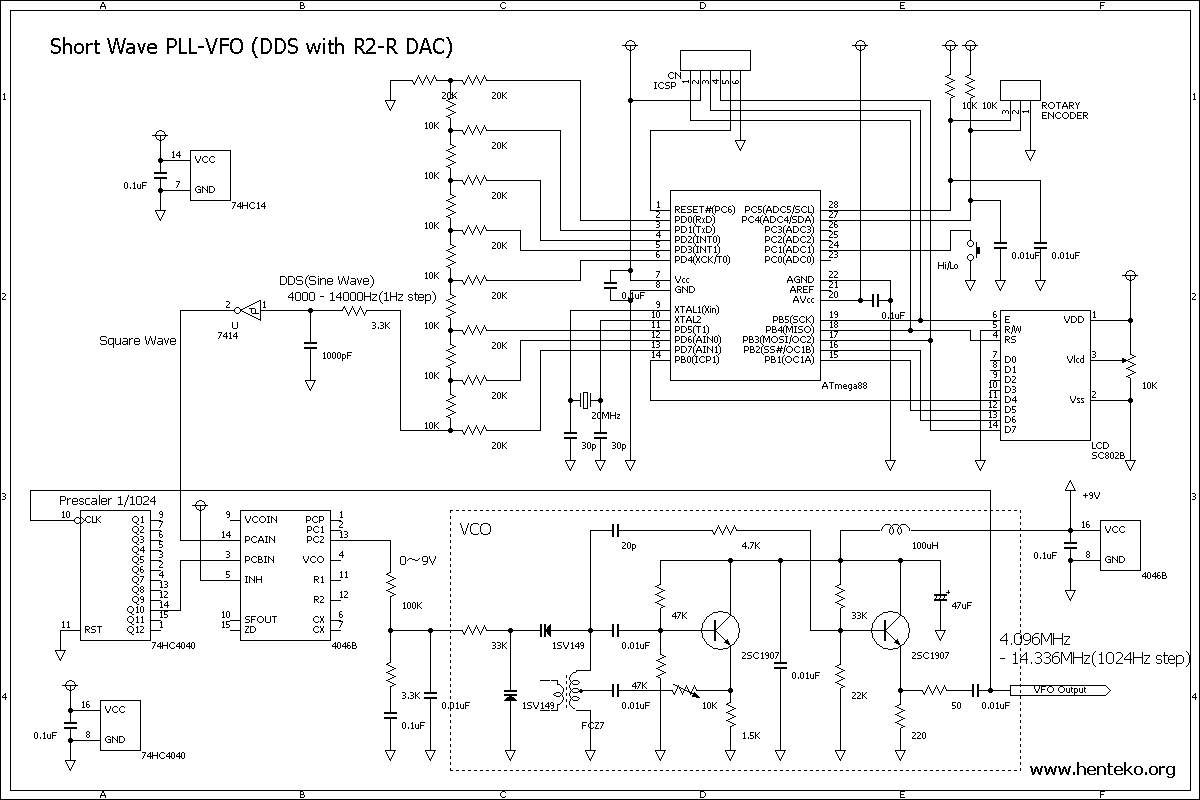

最終的な実験回路は、以下に示します。前回と比べてDAC(R-2Rラダー抵抗回路)、ローパスフィルタ(CRフィルタ)および波形整形回路(シュミットトリガインバータ)を追加しました。

AVRのソースプログラムです。AVRStudio4とWinAVR(gcc)で作成してあります。サンプリング周期で割り込みのかかるTimer1のコンペアマッチ時にサイン波形テーブルからPORTDに出力する部分を変更しました。

2件のピンバック

AVR-DDSでPLL-VFOの実験 | henteko.org

PIC-DDSの基礎実験 | henteko.org

コメントは現在停止中です。