AVR-DDSを使ったツートーンジェネレーターの製作

※実際にSSBトランシーバーの製作で使用しました。(2015-02-09)

SSBトランシーバーの自作等で増幅回路の直線性を確認するときに利用するツートーンジェネレーター(2トーンジェネレーター)を製作します。ネットで情報をあさるとオペアンプを利用した発振回路を2信号分作成して合成をした回路を見かけます。ただ、オペアンプで作ると周波数の大きな変更が難しいので、いろんな周波数を組み合わせることが難しくなります。PICやAVRなどによるDDS方式で2波を発生させるツートーンジェネレーターなら発振周波数の変更が比較的自由になるので、この方式で作成することにしました。(ツートンジェネレータを使用したことがないので、よくわからないのですが、発振周波数の組み合わせが自由に変更できることにメリットがあると仮定しています。)

PICやAVRで直接DDS方式で交流信号を得るのは、「PIC-DDSの基礎実験」や「AVRを使ったDDS方式低周波発振器の製作」でノウハウがあります。AF帯とはいえ綺麗な正弦波を発生させるためにはサンプリング速度をできるだけ稼ぐ必要があるので、今回は、高速動作に有利なAVRを使用することにします。

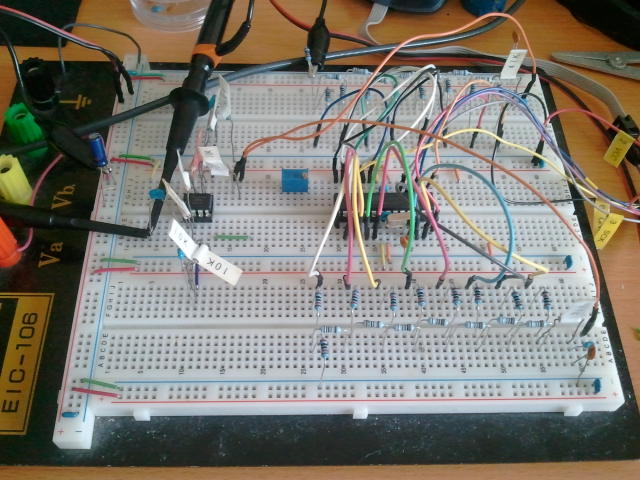

ブレッドボード上でAVRのATmega88Pを使用して実験しました。DAC(DIgital to Analog Converter)は抵抗を利用した8ビットのR-2Rラダー回路です。AVRは、8ビット分のポートを2セット使用してそれぞれ別のDACで2波を発生させ、オペアンプの加算回路により合成しています。(アナログ合成)

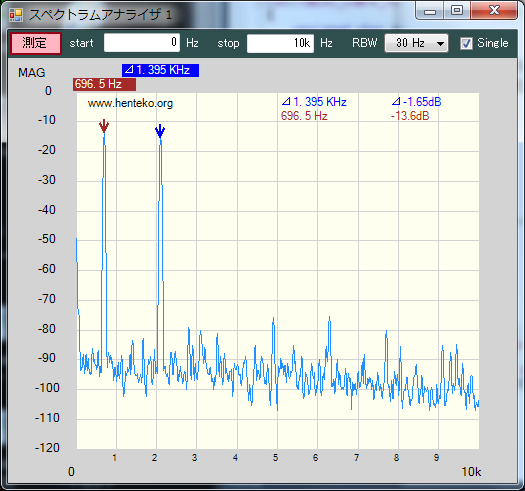

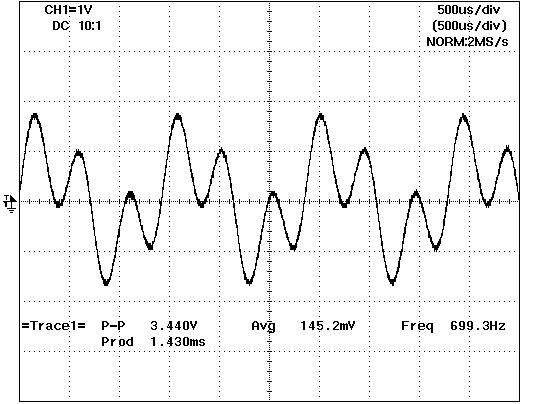

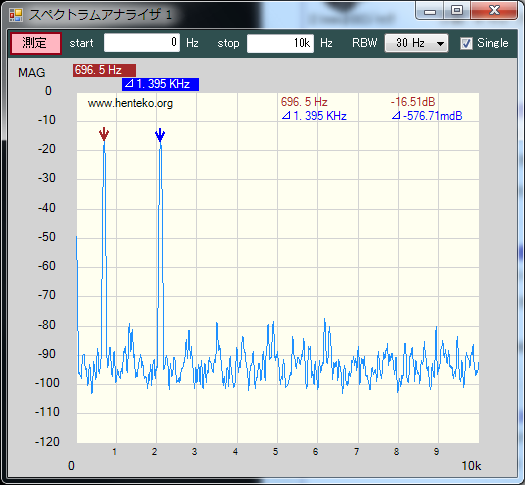

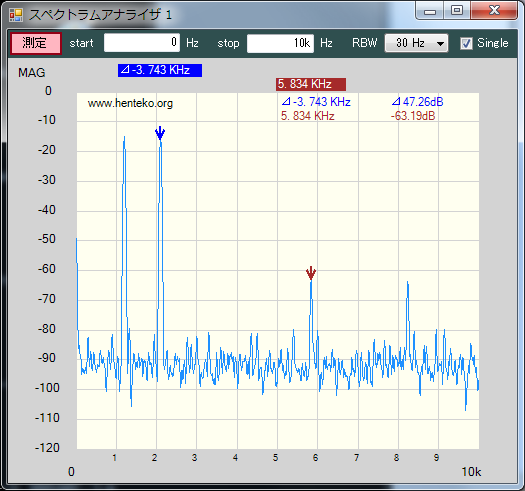

700Hzと2100Hzを出力したスペクトラムをAPB-3で確認します。APB-3は、このようなAF帯も問題なく測定することができるので便利です。スプリアスがやや多く見えますが、発振信号から60dB以上は低いので問題ないと判断しました。CRローパスフィルターのカットオフ周波数を2KHzとしているので全体的に右下がりのスペクトラムとなっています。

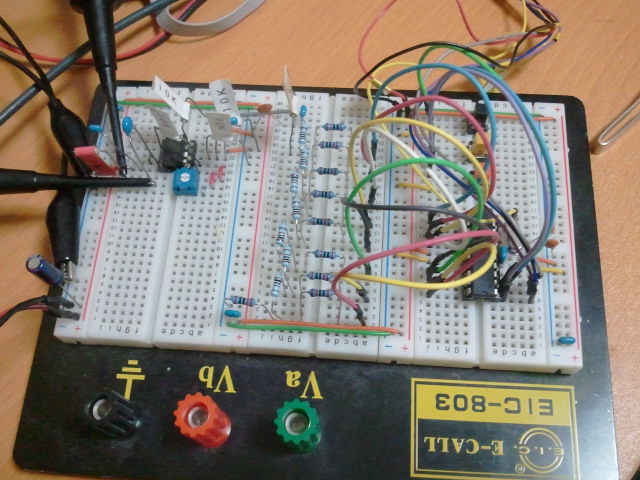

DDS2系統の波形信号を、あらかじめAVR内部で加算処理して合成波を出力する方式(つまりデジタル合成)にすればDACは1回路ですみます。8ビットポートも1系統ですむため、ピン数の少ないAVRを使用できます。20ピンのATtiny861Aに変更して実験してみました。

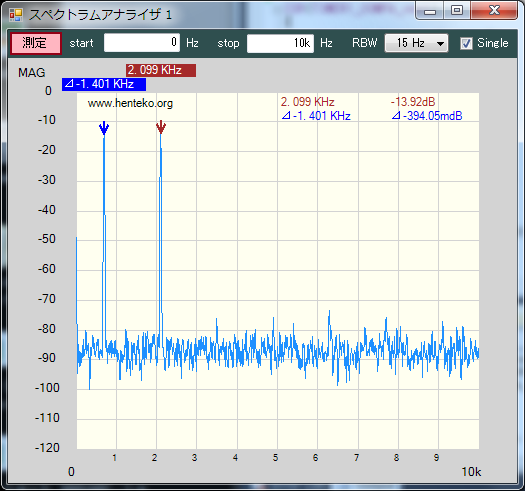

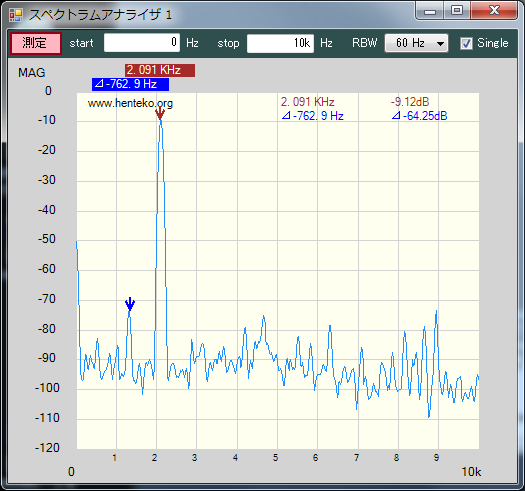

700Hzと2100Hzを合成出力したスペクトラムです。CRローパスフィルターを見直したのと、オペアンプによるアンプとバッファ(ボルテージフォロア)を入れているので、全体としてノイズフロアが上昇していますが、2波出力後の合成と大きな違いはなさそうです。

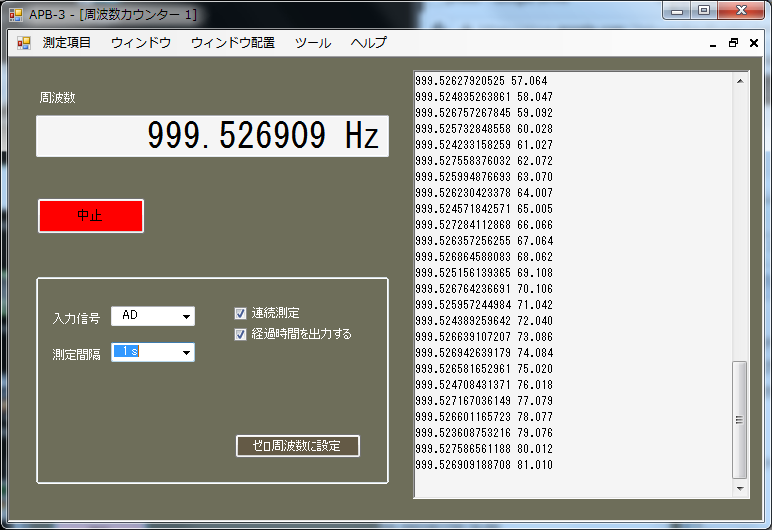

DDS方式なので、発振周波数の精度や安定度は、AVRのクロックに使用している水晶発振子の精度や安定度に左右されます。2波の周波数を同じ1000Hzにして、APB-3で発振周波数を測定してみました。当然のことながら正確で安定しています。10分程度見てみましたが、小数点以下2桁まではまったく変動はありません。ただし、通常、ツートーンジェネレーターに、ここまでに精度や安定度は必要ないでしょう。

ここまで、DDSのサンプリング速度を160KHzとしてきましたが、この速度では、AVRで実行したい他の機能に影響がでるので、サンプリング速度を下げる必要がありました。DDSで生成する最大周波数は3KHz程度なので、サンプリング定理から考えても10倍以上の40KHz程度のサンプリング速度で十分かと思い試してみると、とても実用になるものではありませんでした。サンプリング速度が80KHz以上ならAPB-3で見たスペクトラムに大きな違いは感じられません。ただ、APB-3には、アベレージング(平均化処理)がないので、ノイズレベルの比較が困難です。

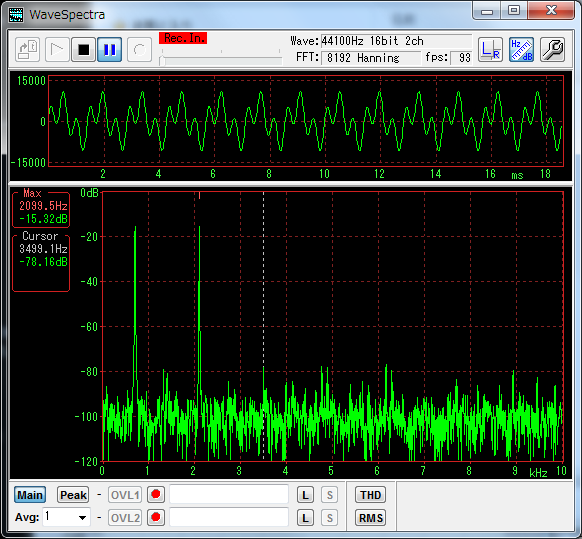

AF帯のスペクトラム測定は、パソコンのWaveSpectraがあります。APB-3とWaveSpectraのスペクトラムを比較測定してみました。信号レベルは、WaveSpectraが1dB程度高めに測定されますが、ほぼ同じようなスペクトラムが観測できます。WaveSpectraには、ひずみ率計算やアベレージングがあるので高度な測定が可能です。

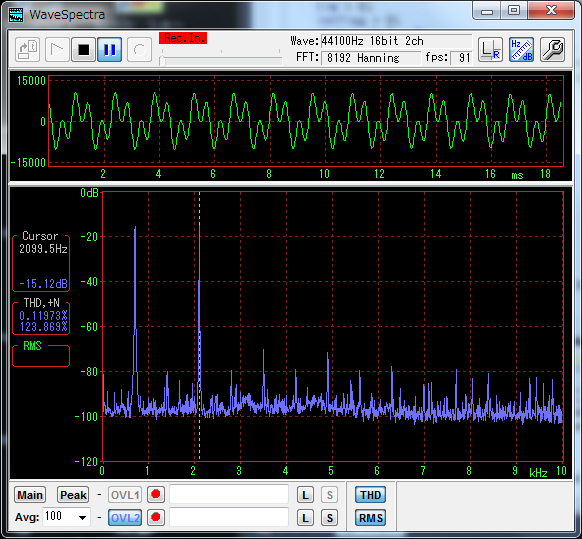

WaveSpectraのアベレージングで、サンプリング速度によるノイズレベルの変動を見てみました。最初は、サンプリング速度160KHzです。2100Hzの全高調波ひずみ率は、0.119%となりました。

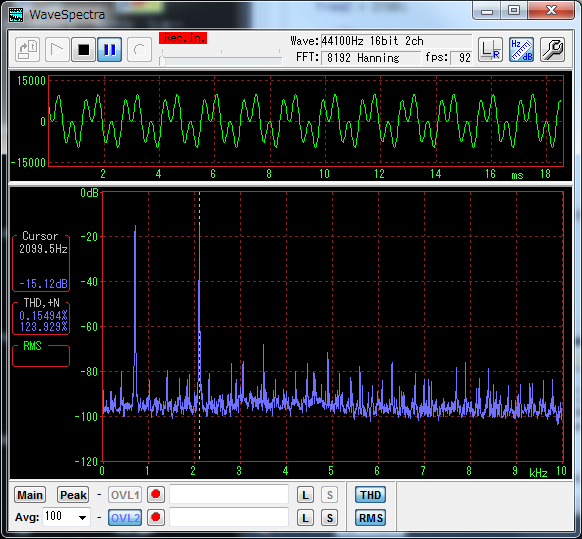

サンプリング速度80KHzです。APB-3では、大きな違いはわかりませんでしたが、全高調波ひずみ率も0.154%と悪くなっています。全体として細かなスプリアスが見られます。ただ、発振周波数とサンプリング速度の組み合わせで位相ノイズが大きく変化するため、この結果だけでは判別できません。しかし、他の発振周波数の場合も、細かなスプリアスの増加が目に付きます。

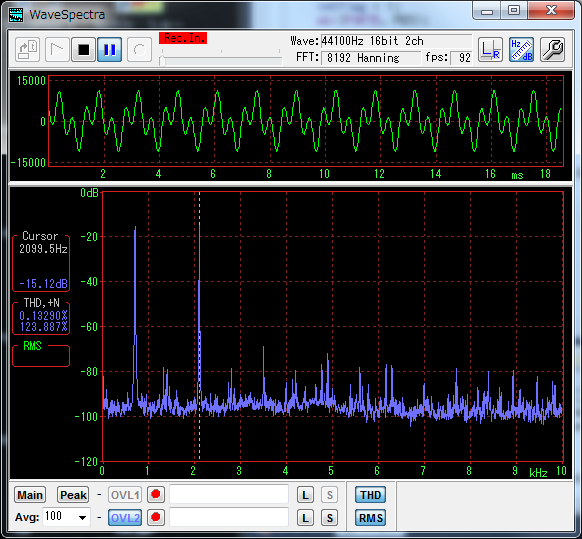

サンプリング速度100KHzです。全高調波ひずみ率も0.132%とサンプリング速度に応じた結果になりました。ノイズレベルも160KHzと大きな違いは見られません。AVRの処理も十分な余裕があります。これらの結果から、最終的にサンプリング周波数100KHzとしました。

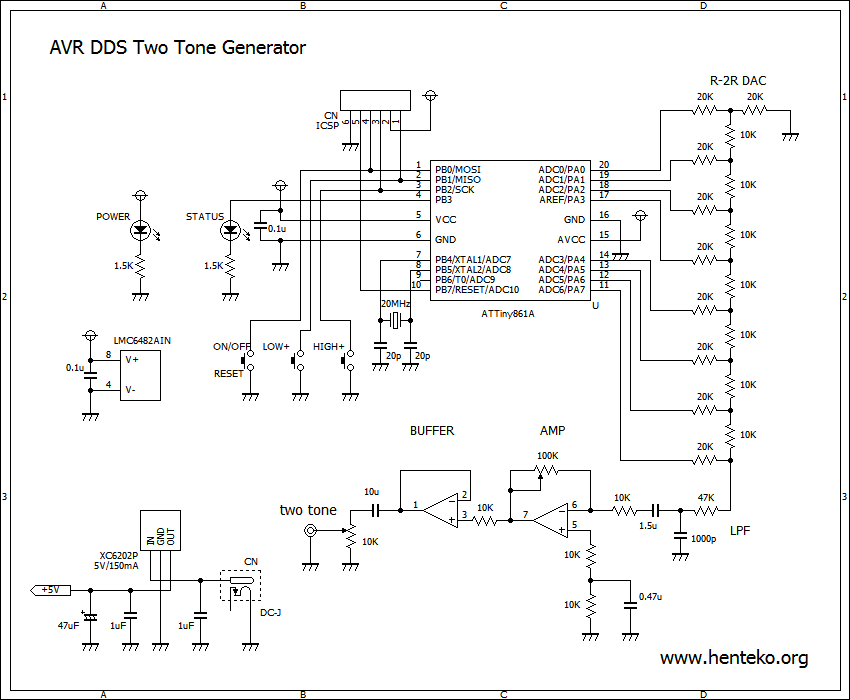

回路図です。出力スペクトラムから判別する信号純度は、DAC+CRローパスフィルターのみが一番良い結果が得られます。しかし、この状態では、出力インピーダンスが高いので低インピーダンスの負荷を接続することができません。したがって、オペアンプで増幅し、さらにボルテージフォロアのバッファを入れました。ここで使用するオペアンプは、入力もrail-to-railに対応したものが必要です。今回はLMC6482AINを選択しました。出力レベル調整のボリューム挿入場所は、アンプ入力やバッファ入力などいろいろ試しましたが、最終的に出力に入れることで一番よい結果が得られました。

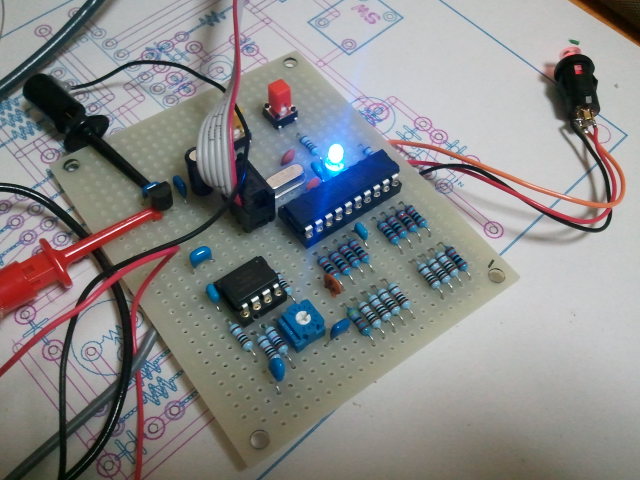

共立電子オリジナルのユニバーサル基板で作成しました。周波数変更するスイッチは、使用頻度が少ないと考えて基板上にタクトスイッチで実装しました。ケース取り付けのLED内蔵プッシュスイッチで出力のオン・オフをします。基板上のLEDは、信号出力時に点灯させます。

ケースは、秋月電子のABS樹脂ケース中サイズです。このケース、以前はポリカーボネート製だったのですが、今回調達したらABS樹脂製に変更になっていました。(以前と比較すると)やや透明度が悪く、くすんだ材質ですが、ポリカーボネートよりやわらかく加工性が良かったです。出力コネクタは、手持ちのケーブル等を考慮してBNCコネクタとしました。

当然のことながら、組み合わせの周波数によってスプリアスの周波数や強度が異なります。これは、1200Hzと2100Hzの2波出力時ですが、5800Hz付近にやや大きなスプリアスが見られます。ただ、これだけ離れれば、SSBトランシーバーのクリスタルフィルタ等で減衰するので大きな影響は無いでしょう。

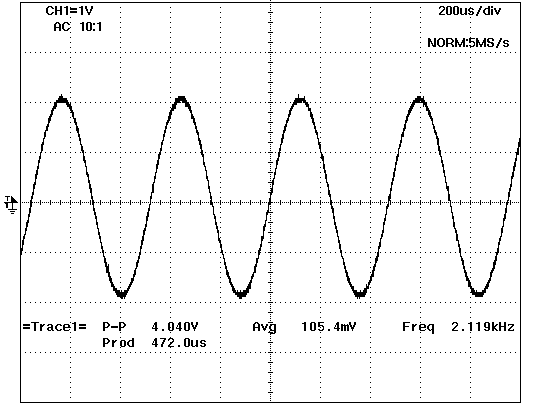

2波の周波数を同じにすれば、シングルトーンのAF発信機なります。初めは波形合成していたのですが、波形計算上、周波数によっては、信号レベルが小さくなることがありました。最終的には、同一周波数時は、1波のみ出力するようにプログラムしました。2波出力時に比べ、理論とおりに信号強度が6dB上昇しています。

AVRのソースコードです。AVRStudio6で開発しました。ツートーンのデフォルトの周波数は、700Hzと2100Hzとしています。周波数は、それぞれのスイッチにより100Hzづつインクリメント可能で、500Hzから3000Hzまで個別に設定可能です。また、出力オン・オフスイッチを長押しすることで、デフォルト周波数にリセットすることができます。2波の合成は、加算して平均化(左1ビットシフト)して求めています。サンプリング周波数は、100KHzとしましたが、200KHzでも動作します。ただし、あまりサンプリング速度を上げると、ほとんどの処理時間を割り込みにとられることになるので、スイッチ入力などの動作が不安定となります。DDSで使用する波形テーブルデータは、1種類で256byteと小さいので通常のSRAM上においています。(ATtiny861AのSRAMは、512byteなので、余裕です。)

1件のピンバック

7MHz-QRP-SSBトランシーバーの製作 | henteko.org

コメントは現在停止中です。